進一步評估了史密斯圓圖上的其他阻抗點下,功放的 P1dB 和功率回退兩種條件下的性能。圖 2a 中的負載條件明顯具有最好的綜合性能,因此被選定用于輸出級設計。最終選擇了 52mA/mm 的偏置電流,并選擇了 8x50μm 器件作為輸出級的基本單元,以滿足功率指標要求。并根據總的傳輸增益指標確定了需要三級放大。

通過依次為驅動放大級和預驅動放大級選擇最佳晶體管尺寸來設計完整的三級功率放大器。這同樣需要仔細考慮設計折中,因為較大的晶體管尺寸可改善整體線性度但會降低 PAE。當所有晶體管的尺寸和偏置確定后,就可以繼續進行匹配和偏置電路的詳細設計。版圖設計從整個設計過程的早期階段就需要開始考慮,以避免不引入過大的寄生效應以及確保設計的可實現性。功放的第一和第二級使用共同的柵極偏置引線(加在引腳 PA_Vg12 上),而第三級設置單獨的偏置引線(PA_Vg3)。這樣就可以單獨優化兩個電壓,以對 PA 的線性度或 PAE 進行提升。漏極供電可以類似地通過兩個獨立的引腳施加+4V 電壓在“PA_Vd12”和“PA_Vd3”上,盡管這兩個引腳在 PCB 板上是相連的。

SPDT 開關采用串并結構,該設計中的串聯和并聯分支中集成了多個晶體管以提高線性度 1。晶體管截止時的電容限制了關斷狀態下器件在高頻率處的固有隔離度,在 28GHz 時開關晶體管的隔離度僅為幾 dB2。減小晶體管尺寸可以改善固有隔離度,但會增加導通狀態下的插入損耗并降低其線性度,因此不是一種可行的選擇。這里采取的方法是采用片上電感補償來改善關斷狀態隔離度。經過細致設計確保導通狀態下具有較低插入損耗,以實現發射通道的高輸出功率和接收通道的低噪聲系數。開關由一個比特位控制電壓“Vctrl1”控制,該位設置為 4V 時表示發射模式、0V 時表示接收模式。“單刀雙擲控制電路”(SPDT 控制電路)可實現單比特控制,該電路本質上是一對二線譯碼器。控制電路和 SPDT 本身消耗的總電流僅 1mA,由“VD_SW”處施加的+4V 電源提供。

接收通道的輸入位于通過 SPDT 連接到兩級 LNA 輸入的“天線”引腳處。接收通道的輸出位于標記為“LNA_RFout”的引腳上。與 PA 一樣,LNA 也具有快速開關賦能電路,使得 LNA 在不工作時僅消耗低至 0.1mA 的電流。低噪聲放大器設計過程的關鍵是找到一種消耗電流低、又具有良好噪聲系數和足夠線性度的設計。

重要的第一步是選擇合適的晶體管尺寸。可使用多個短叉指來減小晶體管的柵極電阻并改善噪聲系數。低噪放的兩級都采用了串聯感性反饋,以使最佳噪聲系數所需的阻抗更接近于共軛匹配和最佳增益所需的阻抗。

低噪聲放大器的第一級以噪聲系數為設計優化目標,但仍需產生足夠的增益才能充分降低第二級噪聲系數的影響。低噪放第二級的噪聲系數并不重要,因此這級設計成比第一級有更高的增益。設計得到的 LNA 僅需要+4V 電源的 10mA 直流電流。柵極偏置電壓施加在引腳“LNA_Vg”上,而+4V 漏極偏置電壓加在“LNA_Vd”上。“LNA_Vsense”引腳則提供對偏置電流的監測。監測到的偏置電流信息可以用于控制柵極電壓以補償例如溫度等環境條件的變化。在正確偏置下,此監測引腳的電壓為 3.9V。使用增強型晶體管的工藝意味著只需要正電源電壓,從而使 MMIC 非常便于系統集成。

仔細的電磁仿真對確保各個模塊良好的射頻性能是非常重要的。采用了逐步添加的方法,每次將電路的一部分加入到 EM 仿真中,而其余部分仍使用工藝設計套件(PDK)中的模型進行仿真。由于集成電路用于二次注塑工藝所得塑料封裝中,所以在集成電路上方注塑的化合物也需要在電磁仿真中考慮。

3. 評估和測試

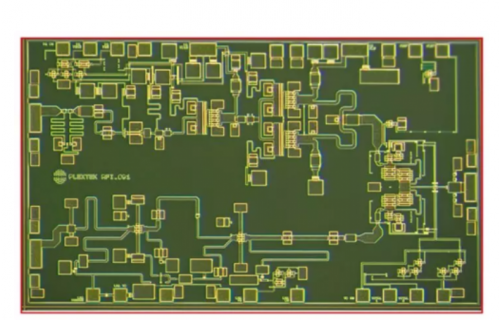

圖 3 是射頻前端芯片的照片。該射頻前端 MMIC 芯片尺寸為 3.38mm × 1.99mm。其焊盤 / 引腳位置與框圖中所示的位置相似,并且它還多集成了多個接地盤,以使其完全可以進行在片射頻測試(RFOW)。它被設計為采用低成本注塑成型 5mm × 5mmQFN 封裝。并且考慮到鑄模塑料的影響,需要精心設計從芯片到 PCB 的射頻過渡界面。設計了定制的引線框架用于實現該過渡,并且封裝體上的射頻端口都被設計為接地 - 信號 - 接地(GSG)界面。

圖 3:28GHz 5G 通信射頻前端模塊 MMIC 的芯片照片

完成加工制造之后,對多塊芯片進行了在片射頻測試,以便在封裝之前確認芯片達成了一次流片即成功的設計目標。這里沒有給出在片射頻測試結果,給出的所有結果都是芯片完整封裝后安裝在典型 PCB 評估板上后測量得到的。

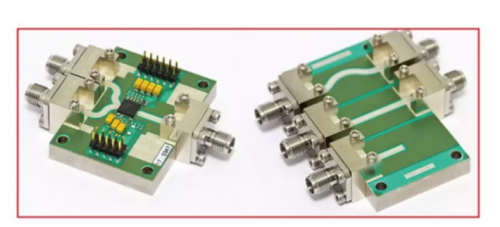

PCB 評估板采用低成本層壓板材料設計,適合大批量生產。將封裝好的射頻前端模塊樣品組裝到 PCB 評估板上;所有測量的性能都校準到 PCB 評估板上的封裝引腳處,從而包含了芯片到 PCB 過渡結構的影響。設計了 TRL 校準單元來將測量的性能校準到封裝的參考面。圖 4 顯示了 TRL 校準 PCB 板,以及一塊 PCB 評估板的照片。

圖 4:封裝好的射頻前端模塊驗證板和 TRL 校準板照片

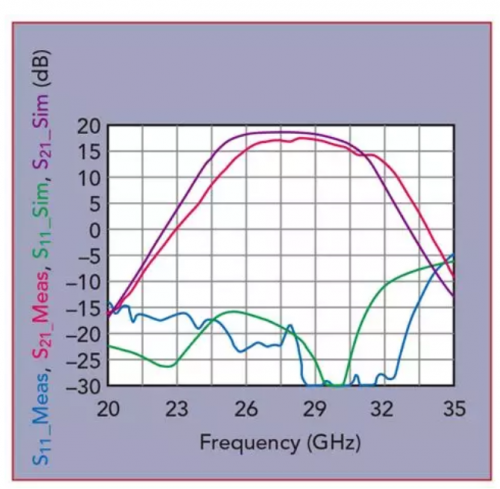

射頻前端模塊 MMIC 安裝在 PCB 上,并以封裝的射頻引腳為參考面獲取驗證結果。在驗證過程中使用市售的多通道 DAC 和 ADC 芯片來控制和監測射頻前端模塊。該射頻前端模塊不需要任何負電壓,因為它采用的是增強型工藝。圖 5 給出了一個典型射頻前端模塊的發射通道的測量與仿真 S 參數的比較。測量數據和仿真結果相當吻合。在此模式下,LNA 被關閉,SPDT 控制位“Vctrl1”切換為高電平,而 PA 則偏置在+4V 電壓下約 70mA 總靜態電流。從 27 到 29GHz,小信號增益(S21)為 17.1dB±0.4dB。輸入反射衰減(S11)在整個頻段優于 18dB。由于輸出匹配是按功率回退條件下最佳 PAE 設計,而不是最好的 S22,盡管如此測量到的 S22(未給出圖示)在整個頻帶上為 8dB 或更好。

圖 5:射頻前端模塊的發射通道的小信號性能測試與仿真對比

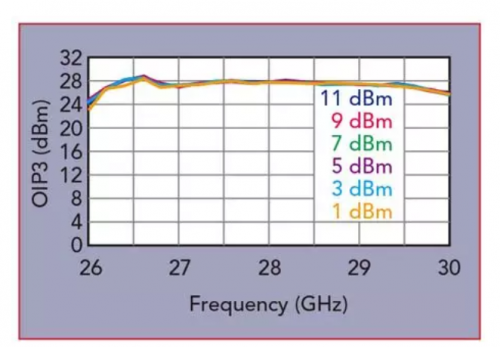

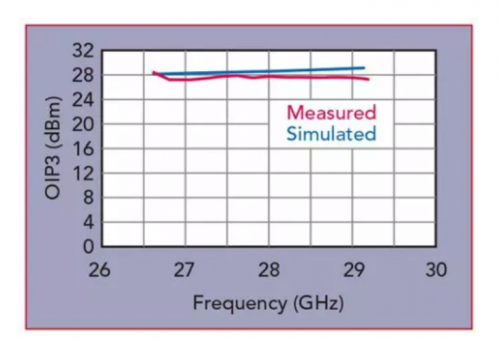

以輸出為參考的發射通道的三階截取點(OIP3)以 100MHz 的頻率間隔進行評估,以反映 5G 系統中的寬信道帶寬。圖 6 是典型射頻前端模塊的實測 OIP3 與有用頻率的功率之間的關系圖,其功率范圍從 1 至 11dBm。可以看出該 5G 頻段上的 OIP3 約為+28dBm,有用頻率功率在 10dB 范圍內變動時,OIP3 變化很小。測量到的和仿真的 OIP3 與頻率的關系如圖 7 所示,具有良好的一致性。

圖 6:射頻前端模塊發射通道的 OIP3 與頻率和輸出功率的關系(100MHz 的頻率間隔)

圖 7:測得的和仿真的 OIP3 隨頻率變化的比較